## E3S

ANNIVERSARY EDITION

### SEMICONDUCTOR & ADVANCED PACKAGING

New thin film solutions – from next-generation glass core IC substrates to Si & WBG Power

### COMPOUND & PHOTONICS

From Quantum Computing to Metalenses, Micro LEDs to Solar Cells – Get the latest news

LAYERS magazine is produced by Evatec AG, Hauptstrasse 1a, CH-9477 Trübbach, Switzerland. All information is correct to the best of our knowledge at the time of going to press. Product descriptions, photos and data are supplied within the brochure for general information only and may be superseded by any data contained within Evatec quotations, manuals or specifications. Evatec AG cannot be held responsible for any errors or omissions.

Electronic distribution from November 2024. Printed distribution from December 2024.

For any comments or queries contact allan.jaunzens@evatecnet.com. ©2024 Evatec AG. Editor-in-Chief: Allan Jaunzens. Editors: Beatrice Eichmueller & Anna Bicker Design: Darren Stacey / Doubletake Design Ltd. (UK). Photography: Peter Fuchs / www.fuchs-peter.ch

## Contents

#### 02-03 Welcome

CEO Andy Waelti reflects on the last twenty years and anticipates what the next twenty might bring.

#### 04-33 Corporate

Hear our CTO's views on innovation, read about the work we have been doing on PEALD, and how our operations grew developing new approaches to assembly.

## 34-69 Semiconductor & Advanced Packaging

Next-generation IC Substrates, new greener solutions in PCB manufacture, and the latest front-side thin film processes for power devices – it's all in LAYERS 8.

#### 70-101 Compound & Photonics

From quantum computing to metalenses and BAW solutions for 5G and beyond, our thin film solutions help you innovate and manufacture at the lowest cost of ownership.

# Reflecting on the last 20 years and anticipating the next 20

O)X(

0)(()

011(0

0))((0

D)X(c

O) K(U

O))((e)

O)X(o)

01K(N

01/(01

(O) ((a)

As we celebrate two decades since the establishment of Evatec in 2004, I take immense pride in our journey so far and the team we have assembled.

Our competencies have grown not only at our Truebbach headquarters, but also across our global organization, positioning us as the reliable long-term partner our customers rightfully expect. Our unwavering commitment to being a "thin film powerhouse" has been the right one and continues to be so, but that does not mean that we do not react to a changing world by continually refining our internal organization, capabilities, and workforce.

Having a profound knowledge of devices, their technology, with market intelligence and employees with skills to identify the needs and expectations of customers two generations ahead is just one example of the goals we set for ourselves. As you explore this year's LAYERS, keep an eye out for the "Who is Evatec" icon – giving a glimpse into some other priorities we set for our company.

New Thin film technology is more essential than ever to deliver mass market consumer devices and applications for the next decades at the right performance and costs – from new panel solutions on CLUSTERLINE® 600 supporting advanced IC substate technology, to new BAW filter solutions for 5G and beyond, enhanced MicroLED technology for Augmented Reality on CLUSTERLINE® 300, and new material development for Heterogeneous Integration, High Performance Logic and Memory.

So here's to our journey over the next 20 years and more, it's one we very much look forward to making together with you, our valued customers.

**Andreas Waelti CEO**

## EVATEC CORPORATE NEWS

| 06 | Navigating innovation: A conversation with our CTO  Dr. Carlo Tosi                           |

|----|----------------------------------------------------------------------------------------------|

| 10 | Dynamic Dragons: Powering Through Asia with Our Prowess Kevin Chen                           |

| 14 | "Ship and Merge" – Enhancing flexibility to meet customer demand Patrick Mathys              |

| 18 | PEALD: The new kid on the CLUSTERLINE® block Dominik Hartmann & Dr. Joerg Patscheider        |

| 22 | Seamless machine relocation services for your Evatec equipment  David Dietsch                |

| 26 | ECL – Supporting customers with thin film coating & characterization services  Philip Zeller |

|    |                                                                                              |

Our market organization is ready to serve you!

Ralph Zoberbier, Admir Asanoski & Jakob Bollhalder

## Navigating innovation: A conversation with our CTO

We have made internal changes to equip ourselves for the future. Our Chief Technology Officer (CTO), *Dr. Carlo Tosi*, talks about balancing tradition and change, overcoming technical challenges and how his team approaches innovation.

## Can you share some highlights from your background and career journey that led you to the role of CTO at Evatec?

Sure, I'd love to share my journey with you. My academic background is in physics and material science and engineering, which I studied in Italy. I then worked at the Universities of Trent and Florence and at the National Institute for Nuclear Physics before moving to Switzerland. The early part of my career was dedicated to thin films and coatings for tribological applications. I soon moved into the world of semiconductors, focusing on thin film and bulk semiconductor radiation detectors for high energy physics applications. My transition from the academic world to business happened smoothly when I joined Oerlikon Solar in Switzerland. At Oerlikon, I started with the development and transfer of the PECVD production processes from the headquarters' pilot line to the customer's factory, and eventually, I ended up overseeing the integration of all the processes in the production line. This role involved the transfer of production processes globally, which was interesting and challenging! From there, I moved to ALSTOM and joined the Future Technology organization as Group Manager Innovative Components. This was an exciting time as I was part of a team that implemented an open innovation approach to scout new technologies and solutions for

future business. This was a particularly insightful experience and taught me a lot about innovation. Subsequently, I joined ABB Semiconductors as a Technology Manager, where I was responsible for the development activities related to bipolar power devices. This role included regular travel between sites in Switzerland and the Czech Republic, with a focus on improving communication and collaboration between the two development teams. Finally, in 2019, I joined Evatec as a Product Marketing Manager, a role that, although businessoriented, required significant technical knowledge. After a period of time as the BU Semiconductor leader, I had the opportunity to become Evatec's CTO, rounding off my career journey wonderfully.

#### What has shaped your leadership style?

Overall, my leadership style has been shaped by a combination of technical expertise, adaptability, project and product management skills, business orientation and an understanding of the importance of open communication and collaboration. Every little detail can have a big impact when it comes to being successful, and blending creativity with careful execution is essential to successfully complete projects and respond to market needs.

#### Who is Evatec...

#### **R&D** at Evatec

#### Technology & Market Understanding:

Taking the right decisions in time comes from profound knowledge of devices, their technology, market intelligence and our employee's skills to identify the needs and expectations of customers two generations ahead.

#### **Innovation Strength:**

A strong technology portfolio exploits synergies across our markets giving stand out solutions for our customers that put them ahead of the pack.

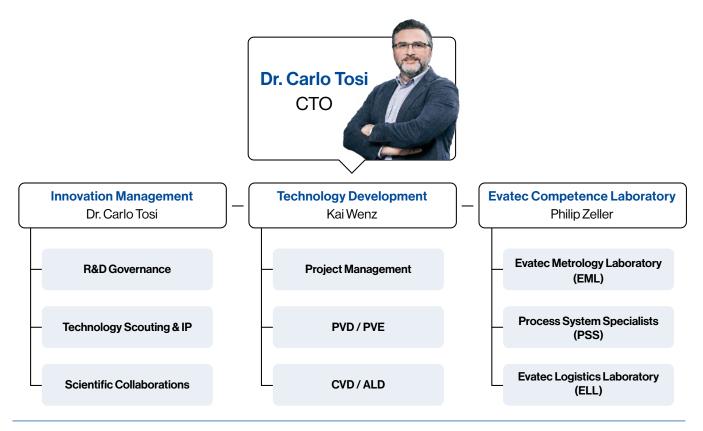

CTO Organization at Evatec

## What aspects did you inherit from the former CTO, and how have you built upon or transformed them?

He left behind an amazing team, and since taking over I've prioritized fostering an environment where each team member can use their skills and talents to the fullest.

## What were the challenges after starting in your new role as CTO, and how did you address them?

The biggest challenge was a major reorganization of our company, including the CTO department. We had to focus on a smooth transition from the old organization to the new one in the initial weeks. We addressed this by defining our innovation process and the procedures necessary for our daily efforts, while at the same time not losing sight of our ongoing development projects. We also worked hard to bring our laboratory operational standard to the highest level. It's a continuous effort and there's much work still to be done. Our goal is to continually innovate not only our products, but also the way we navigate through innovation.

## What strategic goals or innovations do you envision for your department?

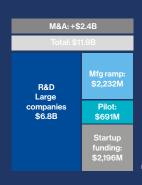

The semiconductor industry is always on the move, breaking barriers and setting new standards at a rapid pace. This evolution is driven primarily by aggressive investments in research and development. Can you imagine that almost 20% of the industry's annual revenue in the US is funneled back into R&D? We are talking about tens of billions of US dollars. As a supplier, we at Evatec know-how critical it is to keep up with this whirlwind of progress. But we don't just want to keep up. We want to lead. And that's why our number one goal is to always be at the cutting edge of our markets.

It's pretty amazing to think about how much digital computing has become a part of our everyday lives. It's all due to the incredible advances in hardware and software. And it's not just that - so many other technologies are also growing at an unbelievable pace. Just think about it - analogue electronics, memory and storage technology, advanced communication solutions, not to mention Al and energy generation and transformation. It's an exciting time to be in this industry.

Evatec already has a strong footprint in the discrete device market. We're talking about Wireless, MEMS, LED, AR, Power and so on. But that's not all. We're continuously growing our product base and refining our process solutions using the latest advanced process control techniques.

However, we're not just focusing on these areas. We're also keen to enhance our solutions for the CMOS frontend of the line, which includes both the front side and the back side of the wafer. For that we are currently working on several development projects, in collaboration with major market players, which will allow us to penetrate the memory business, for example. Packaging and interconnect solutions are also vital. That's why we're paying close attention to emerging trends such as chiplets, 3D integration, and fan-out wafer-level packaging (FOWLP).

Last but not least, we want to do all this following the best innovation and project management standards in order to provide our customers with the quality they expect from a Swiss company. For this, we've created a specialized team to oversee innovation governance, ensuring our customers receive nothing but the best.

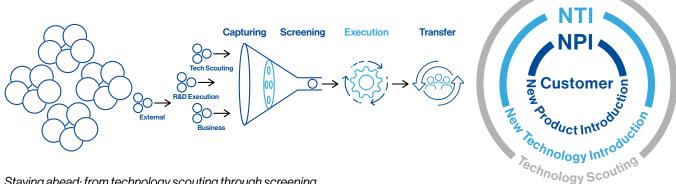

Staying ahead: from technology scouting through screening all the way to the best product or technology introduction.

## How does your team approach innovation and what processes or frameworks guide idea generation and implementation?

Well, I'll try my best to keep the explanation brief. The R&D Department is composed of three teams, namely "Innovation Management", "Technology Development", and the "Evatec Competence Laboratory". Innovation Management is further structured into three parts: Governance, Technology Scouting & Intellectual Property, and Scientific Collaboration. Basically, Governance is where we define the way Evatec goes through the innovation process. For example, we have structured the Technology Scouting process, the New Technology Introduction (NTI) process and we largely contributed to the redefinition and implementation of the company's New Product Introduction (NPI) process.

At Evatec, everyone can come up with an idea, which could potentially become a development project. All you have to do is present your proposal to the Technology Scouting team. They will assess the proposal's potential and how well it fits with the company's strategy. It's not just technical experts who look at these proposals - business colleagues are also involved. If the proposal passes this screening phase, it might become an NTI project or be framed as an NPI project.

However, only the Product Marketing Manager can submit new product projects (NPI) to the Executive Board. That's because all NPI proposals need to get the buy-in of at least one of our two business fields either Semiconductor & Advanced Packaging, or Compound & Photonics. The idea is to ensure that our innovation efforts are always linked to a return on investment.

Now, we also work with external partners on innovation initiatives. These collaborations are managed by the Scientific Collaborations team. They're in charge of finding new partners and proposing new collaborations.

Moving on, the Technology Development team is where the development projects come to life. The team is staffed with project leaders, engineers, and scientists, and it's they who hold all of Evatec's core PVD/PVE and CVD/ALD technical knowledge.

And of course, we have the Evatec Competence Laboratory (ECL). It's like our playground, equipped with over 30 vacuum deposition systems, representing all of Evatec's platforms, and more than 40 in-house metrology tools, including SEM, AFM, XRD, etc. It's essentially one of the best equipped labs around! We also have a chemical lab to aid our everyday work. We use the ECL for all sorts of things, like hardware, software and process development activities, customer demo and sampling, product maintenance, engineering initiatives, and a whole lot more.

So, that's a nutshell view of our R&D Department. I hope this gives you a general idea of how we're organized!

## Give us an example of significant technical challenges your department has overcome?

The team is constantly delivering great results, but I have to give a special shout-out to our PEALD initiative. This was a brand new technology for us and we've managed to develop and launch it successfully. One module is already docked to a CLUSTERLINE® of one of our customers. Right now, we're refining our solution which includes in-situ cleaning. We really think that our PEALD can be a game changer for a variety of applications, especially in a cluster configuration, where you can mix PEALD, PECVD, PVD, and etching all in one system.

#### What excites you most for the future?

The investment we have made in optimizing our internal innovation processes is starting to pay off and we can focus better on execution of all the projects we have now prioritized, bringing new technologies or processes to market more quickly. There are so many fields where my team sees huge potential. I feel like "a kid in a candy store" so don't be surprised when we bump into each other in the corridor at our headquarters and you see me with a big smile on my face!

You can read more about **PEALD on page 18** in this edition of **LAYERS**

## Dynamic Dragons: Powering through Asia with our Prowess

Discover how Evatec developed its organization in Asia and the key role the region plays in the company's growth. From cutting-edge solutions to collaborative partnerships, find out more about Evatec's journey in the dynamic Asian market with *Kevin Chen*. Head of Evatec Asia.

## Can you share the story of how Evatec established its organization in Asia?

Evatec established its first Sales & Service Organization (SSO) in Asia in 2016, starting from South East Asia (Singapore, Malaysia) and expanding to Taiwan, China, and Japan. The SSOs provide direct customer support, enhance understanding of customer needs, and strengthen cooperation and partnership with them directly.

#### What motivated the company to focus on this region?

Asia's robust market for Semiconductor, Advanced Packaging, Optoelectronics, and Photonics presents significant business opportunities for Evatec. It's our biggest market. The region's mature and cost-effective supply chain, coupled with its advancements in relevant technologies, contributes to Evatec's growth.

## What do the people like about working for an international company like ours?

Working for an international company like Evatec offers the opportunity to collaborate with people from around the world in a multi-cultural environment. It also provides exposure to cutting-edge technologies, broadening our perspectives. Swiss quality standards facilitate trust and long-term partnerships with colleagues at our Swiss headquarters.

## How has Evatec adapted to the challenges presented by the Asian market?

We need to support different customer types – OSATs (Outsourced Semiconductor Assembly and Test), IDMs (Integrated Device Manufacturer) or Design Houses and their different needs. Of course, there is always strong competition, so we also need to

differentiate ourselves. Our Asia Sales & Service Organizations (SSO) have invested heavily in training and transferring know-how to our Asia team members. We are able to provide professional and fast responses to customers. As a company Evatec has also developed relationships on the supply chain side with local Asia experts.

#### Tell us more about the services of the Asia SSOs?

The main activities of our SSOs are providing sales, marketing and technical support to our local customers. In partnership with our colleagues at Evatec HQ we are continuously looking to develop our Asia business further. Typical day to day activities include a very wide range of tasks, such as promoting Evatec's technologies and products in meetings with customers or in any kind of technical forums or trade shows. We provide services like machine installation, trouble shooting and performance improvement. Collecting customer's feedback as well as market intelligence allows us to support our company in developing the best solution for our local market.

SPARE PART warehouses in 5 countries

>>>>

## How has the organization changed over the recent years and what impact has it had on customer satisfaction and business growth?

Back in 2016 when we started out our local know-how was in its infancy, and we had to rely more heavily on support from our Headquarters in Switzerland. However, in 2019 we started to build up the ATTF (Asia Technical Task Force) and an Asia L2 (Level 2) support team in cooperation with our senior management from HQ. We then established an Asia Software Team. TMM (Technical Marketing Management) Team and a Trainer Pool in 2020. Even during the time of the COVID-19 pandemic (2020 -2022), we continued investing in Asia to strengthen our capability to better serve customers and grow our business. Going forward, we will keep investing in selected Asia sourcing activities to strengthen our support for Asia customers. With all the resources (engineering team, spare parts warehouse, service office etc.) we have invested in Asia, our customers can now get more professional and faster technical support from Evatec than ever.

## You now have around 140 team members and 13 offices. How have you managed to foster collaboration and knowledge sharing among team members as the organization grew?

We work with common processes around the world with clear rules and regulations for our new Asia team members to follow. In addition, starting from day one, we introduced and encouraged a "One Asia Team Concept" when we set up the Asia SSOs in 2016. Therefore, our Asia team members who are in different countries share the same work culture and values as a single team. It's all about bringing the right people on board and supporting their integration.

#### Tell us about the "One Asia Team" Concept and what that means?

The "One Asia Team" spirit is that all employees of our Asia SSOs belong to one big Asia Team. People may still spend the majority of their time working in their home country, but will still need to provide service outside their base location and work together with other colleagues in different countries for specific projects when there is a need. The concept provides lots of benefits for the company as well as our Asia team members such as more flexibility in using our Asia resources to support projects or countries where we need lots of short-term manpower or special expertise. We cooperate closely to manage business using talents we have across the whole team. We share our knowledge and experience with each other so we can grow together. People have a chance to get exposure to various cultures and broaden their view of the world. Employees in our Asia SSOs love the "One Asia Team" Concept and enjoy being part of a big Evatec Asia family!

## ≈50% CHF REVENUE in Asia

## What is the role of the Asia Technical Task Force (ATTF) team?

The main tasks for our ATTF include technology transfer from Swiss HQ to Asia, development of local technical solutions, high-skill support (including Asia L2 support, process, software and training), and special project management within the Asia region. Dr. Suresh Singaram leads the ATTF team, which collaborates across Singapore, Malaysia, Taiwan & China.

## Give us an example of an innovation the ATTF team has delivered?

In addition to various technical support functions, the ATTF team spent approximately two years developing and optimizing the eLAT software tool. This tool enables rapid analysis of potential technical issues using machine datalogs. We recognize that user-friendly and powerful software is crucial for successful production equipment. We support our specialists within the HQ in developing new software features and capabilities.

The "One Asia Team" spirit – all employees of our SSOs belong to one big Asia Team.

### 13 OFFICES

in major Asian locations -China, Taiwan, Korea, Singapore, Malaysia and Japan

## ns-

## What emerging trends do you see in our markets in Asia and how is Evatec positioned to address them?

I would like to give feedback from two perspectives: **Technology and Production trends:**

- Technology trends: We see that technology developments such as Artificial Intelligence (AI), Augmented Reality / Virtual Reality (AR / VR), 5G /6G Communication, High Speed / Quantum Computing, Electric Vehicles, happen faster and faster. All require lots of new materials (different wafer or substrate materials), process capabilities (TSV. TGV. WLO. high precision film properties control) and also highly sophisticated machine performance. Evatec invests huge amounts and efforts in R&D activities and in working closely with global key market players / customers (IDM, OSAT, Design House), R&D institutes on developing new technologies which can keep us as a tier one technology solution provider.

- 2. **Production trends**: The increasing geopolitical tension leading to a Supply Chain Management (SCM) move to the south may mean that more and more market players including device manufacturers, material and equipment suppliers increase their investment and production capacity in southern Asia regions like Malaysia, Singapore, Vietnam, Thailand and India etc. However, as a complete region, Asia will keep its leading role. Our own flexible Evatec organization and our mature team can provide professional support to our customers wherever they are.

## ≈140 HEADCOUNT (>100 CS) in Jan 2024

## Tell us about how Evatec collaborates with local partners and suppliers in various Asian countries.

We are focused on system design and component integration. We collaborate closely with suppliers in Asia, including Singapore, Japan, Taiwan and China. We aim to enhance Asia sourcing and customer support activities to better serve our customers in Asia.

## What are Evatec's strategic goals for growing the business in Asia in the future?

Our strategic goals are well-defined and ambitious.

- Market Leadership: We aspire to become the number one player in our served markets. This goal reflects our commitment to excellence and customer satisfaction.

- 2. **First-Class Customer Support:**Providing top-notch support to

customers is a priority. To achieve this,

we collaborate closely with our global

organization, aligning activities to

deliver professional service as a unified

team.

- 3. Expanding into Emerging Markets:

While traditional markets like China,

Taiwan, Korea, Singapore, and

Malaysia will remain strong for us, we

recognize the potential in emerging

regions. We actively participate in

the growth opportunities in Vietnam,

Thailand and India. These countries

are witnessing increased investment

and technological activities, making

them attractive markets for Evatec's

products and solutions.

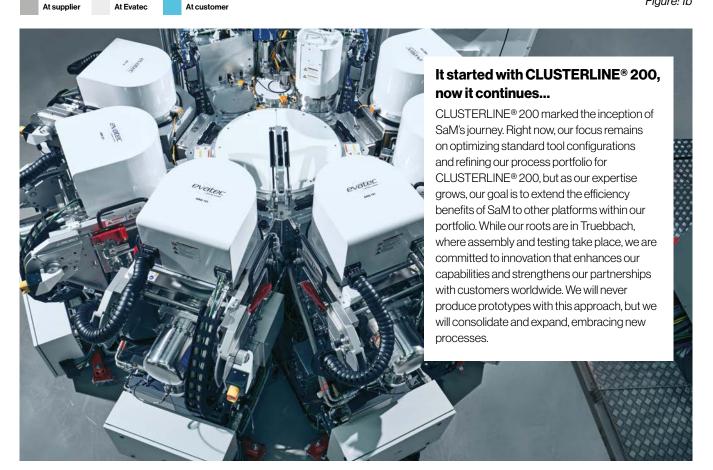

## "Ship and Merge" Enhancing flexibility to meet customer demand

Evatec COO *Patrick Mathys* tells us about Ship and Merge (SaM), just one of the innovative manufacturing initiatives at Evatec supporting our commitment to efficiency and flexibility to meet the needs of our customers.

#### So, what is "SaM"?

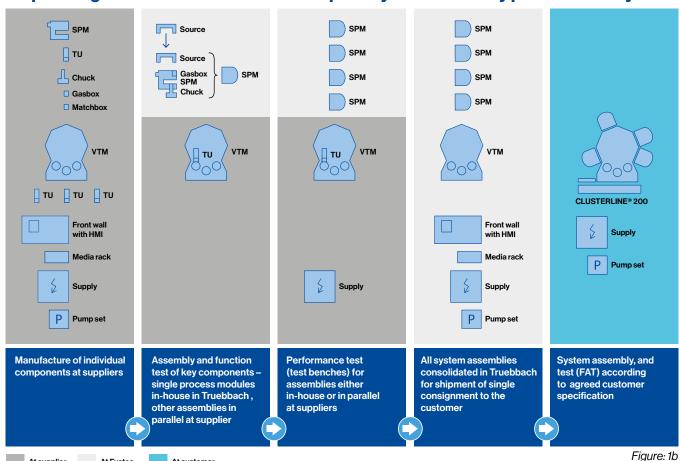

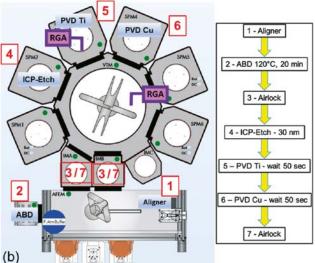

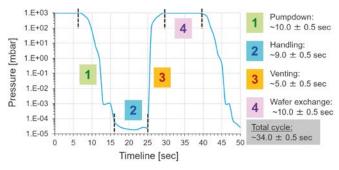

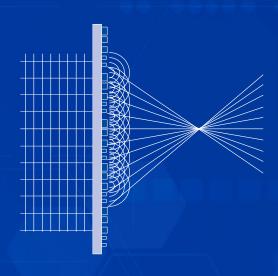

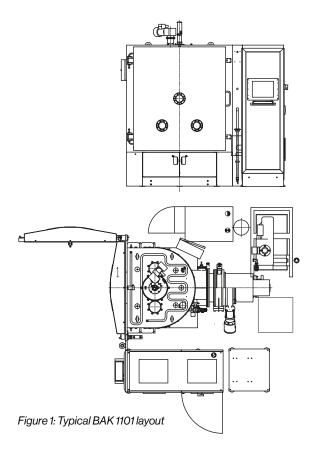

When global demand for electronic components surges and our customers need to react, SaM can step in to help standardize and accelerate assembly, testing, and shipping of the individual core components within the tools we need to deliver. SaM focuses on lead time and cost reduction, space requirements and resources. With SaM, the individual core modules SPM (Single Process Module), VTM (Vacuum Transfer Module) and E-Racks (switch and generator cabinets) of a standard configuration CLUSTERLINE® 200 platform can already be tested and qualified separately with the help of improved and more sophisticated test procedures with enhanced test benches. These can be standard tests for functionality and quality assurance, but also process tests in the case of SPMs. This means that we can dispense with complete assembly of the system in Truebbach. The merging of the entire system then takes place at the end customer's site. The complete shipment as a single consignment from Switzerland means that the customer sees no difference to today's deliveries. Figures 1a and 1b compare a traditional and Ship and Merge approach.

#### **Preparation is key**

To ensure the success of our approach, we undertook a comprehensive restructuring of our assembly and testing processes for a CLUSTERLINE® 200 through a series of subprojects.

In the "pull-in" subproject, we streamlined the ordering process by consolidating core modules at a higher bill of material (BOM) level from our subsuppliers. For instance, a VTM is assembled alongside all Treatment Units (TU) and customized components, while an E-rack comes equipped with generators, including connected cables. This approach aims to significantly reduce assembly time at our facility.

Building upon this foundation, the process testing subproject adds another layer of refinement. Here, the core modules undergo rigorous functional and process tests to ensure they meet predefined standards. For example, the VTM undergoes a marathon test with substrates. In the case of the E-rack, the generators are started, and the power is measured, and single process modules (SPM's) have their gas flow and process parameters recorded. The goal of this thorough testing process is to avoid complete assembly of systems in Truebbach, freeing up space for other customer projects.

Important to note is that the test benches subproject encompasses the development of both hardware and software, as well as the adaption of existing test benches for pull-in and process tests. Notably, a complete new E-rack test bench was developed as part of the initiative and capabilities of our VTM and SPM test benches were massively improved.

#### Maintaining control of process know-how

Although our subcontractors excel at manufacturing, including implementing the new test approach for modules like the VTM and E-Rack, the assembly and testing of SPM's, which embody Evatec's core expertise, remain exclusive to our facility in Truebbach. For logistical efficiency, all individual modules of a system will be sent to Evatec in Truebbach before being consolidated and shipped to our customers as a single consignment.

#### SPM Source SPM Source Chuck ☐ Gasbox ☐ Matchbox VTM TU TU CLUSTERLINE® 200 CLUSTERLINE® 200 Supply Supply Front wall Pump set Media rack P Pump set Media rack Supply Supply Pump set Pump set Manufacture of individual Assembly and function Complete system System dissassembly, System reassembly, packing and shipment and test (FAT) according components at suppliers test of key components assembly, function and like single process performance test (IAT) as single consignment to agreed customer modules in-house in specification according to agreed Truebbach customer specifications

#### Traditional approach including complete system assembly and test prior to shipment

#### **Overall benefits for our customers**

At Evatec

By implementing SaM, we are not only optimizing our own assembly process but also providing significant benefits to our customers. Here are some advantages:

At customer

#### ■ Increased Flexibility

At supplier

SaM enables us to free up capacity in our own assembly line, allowing us to adapt swiftly to changing market conditions. We can react quickly to accommodate the assembly of other tool types beyond those included in the current project. For instance, we can efficiently handle non-standard tools or prototypes tailored to specific customer requirements without compromizing on quality or delivery timelines.

#### ■ Reduction of Lead Times

SaM expedites our operations by optimizing assembly and testing processes, resulting in significant reductions in lead times. This effect is even bigger in capacity constraint times, as the SaM line is independent from the normal assembly line.

#### Quality Assurance and Sustainability

Consistent Quality: With SaM, we standardize test instructions and protocols, guaranteeing top-notch quality across all repeat builds of standard hardware configurations. This ensures that every product meets our high standards, giving our customers "peace of mind" with each purchase.

Shared Insights: Our central database offers valuable insights that benefit everyone involved, from our quality assurance team and purchasing department to our service technicians and, most importantly, our customers. By sharing information and working together, we're committed to delivering excellence in every aspect of our products and services. SaM is already showing its worth!

Within the last twelve months we already shipped 17 SaM systems which we could not otherwise have shipped because of the high order backlog in our normal assembly. As the concept is ready and proven we are now able to expand it further to additional processes whenever we see the need.

Figure: 1a

In essence, SaM isn't just about transforming our assembly process, it's about putting our customers at the center. By streamlining operations, SaM ensures that we can deliver our solutions and tools faster, with higher quality, and with more efficiency than ever before.

#### Ship & Merge eliminates the need for complete system assembly prior to delivery

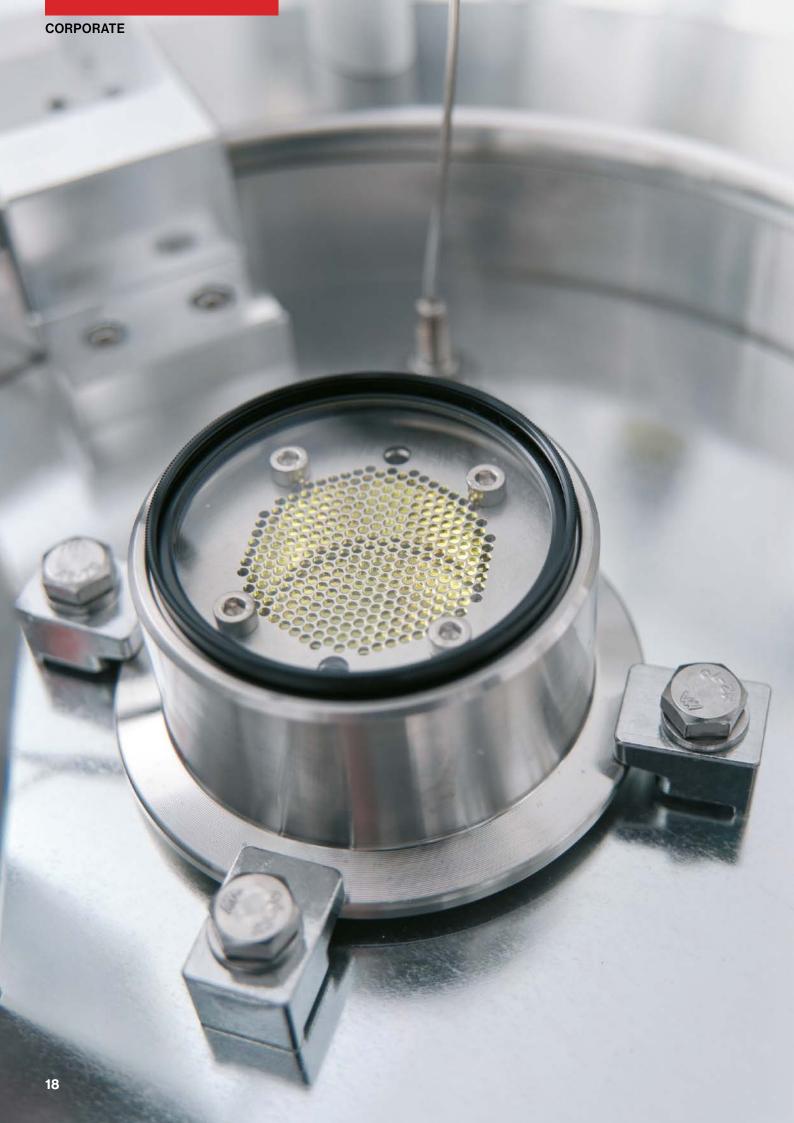

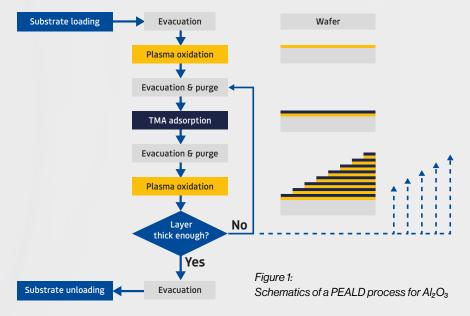

## PEALD: The new kid on the CLUSTERLINE® block

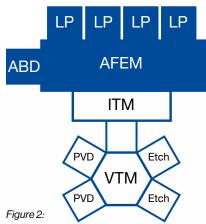

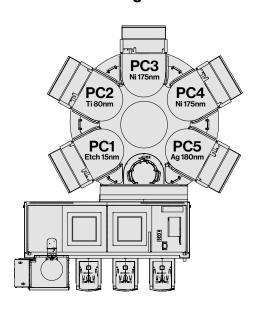

**Dominik Hartmann**, Manager Technology Development & **Dr. Joerg Patscheider**, Principal Scientist, present a new module for Plasma-Enhanced Atomic Layer Deposition (PEALD). As just one of the modules available on the CLUSTERLINE® 200 family, customers can freely combine it in configurations of up to six modules per cluster together with established techniques like sputter, etch and PECVD.

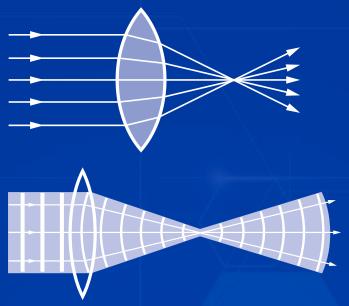

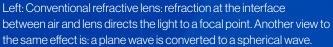

Thin films produced by sputter deposition can be used to address various functionalities such as high optical transparency, defined values of electrical conductivity, specific electromechanical properties such as piezoelectric performance and others. Since sputter deposition is a directional process, it is commonly straight forward to achieve such properties on flat and planar substrates. However, as soon as homogeneous films are required on non-planar surfaces, such as structured wafers and surfaces with radii of curvature much smaller than the wafer dimensions, chemistry-based techniques are well-known for providing solutions to such requirements. Plasma-Enhanced Chemical Vapor Deposition (PECVD) is already well-established in a multitude of applications for films in the thickness range from several hundreds of nanometers up to more than ten micrometers. However, if films thinner than about a hundred nanometers and down to the nanometer range are needed, Atomic Layer Deposition (ALD) and its plasma-supported extension, Plasma-Enhanced Atomic Layer Deposition (PEALD) provides solutions that combine excellent conformality (uniform thickness irrespective of substrate curvature) with atomic precision in thickness.

Evatec's new PEALD module is a novel single-wafer processing station within the CLUSTERLINE® 200 family thats ideal for deposition of thin dielectric films. To reduce deposition temperatures with respect to thermal ALD, a microwave plasma source is used enabling for instance, the preparation of  $Al_2O_3$  films at near room temperature. In contrast to other forms of plasma excitation like RF or even pulsed DC, microwave plasmas have very low sheath voltages. Consequently, the energy of ions impinging from the plasma onto the growing film is only a few eV. This is an important feature if thin film materials sensitive to ion radiation

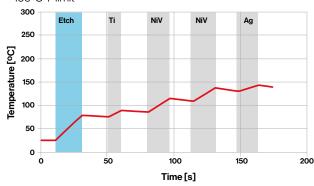

damage need to be deposited. While most materials will not suffer radiation damage at energies below ca. 20 eV, some crucial compounds already show deterioration at lower energies. Examples of ion irradiationsensitive materials are many group III nitrides such as GaN, InN etc., but also sputter-sensitive oxides, e.g. ITO, MoO<sub>3</sub> and other transition metal oxides, as well as sulfides like MoS<sub>2</sub> and other 2D materials. Only microwave-excited plasmas can provide the favorable conditions required. Figure 1 illustrates a typical PEALD process flow.

Where ion radiation damage is not of concern for the user, the new PEALD module can be operated with a radio frequency bias on the chuck, allowing full control over the energy of impinging ions in a wide range from a few eV to more than 200 eV. This option allows tuning of various materials parameters of the grown films such as density, refractive index and microstructure.

The use of an arrangement of high-strength permanent magnets outside the process chamber enables this new module to reach Electron Cyclotron Resonance (ECR) conditions. This leads to very high plasma densities which allow almost complete reactions during the plasma step (i.e. during oxidation and nitridation processes) at low temperatures.

In addition to the substrate biasing possibility, the PEALD module is equipped with a heatable substrate holder for temperatures of up to 500°C. While this is 200°C too high for almost all PEALD processes, post-deposition annealing in-situ is possible with this device. This opens up new ways to tailor selected properties of the previously prepared films without compromising the PEALD deposition process.

The system is set up to use two different metal precursors, which enables deposition of ternary films such as SrTiO<sub>3</sub>, Ta-C-N etc. with varying elemental ratios. Ternary oxides, e.g., ITO as well as multilayer structures of the type ABX (X being a nonmetal) can also be prepared. The design of the module and processes have been rigorously optimized to achieve minimal precursor consumption and reduced cost of ownership. A special carrier configuration allows for two-side deposition of substrates in a single run, while maintaining the same layer thickness on both sides.

To counteract potential issues with particles formation due to deposits on the reactor's inner walls, the module can perform different cleaning processes like plasma-enhanced chemical *in-situ* cleaning procedures.

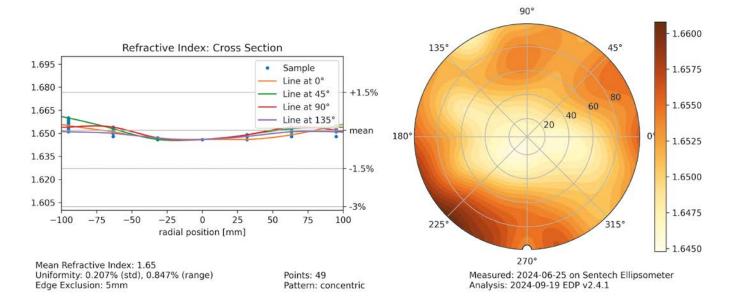

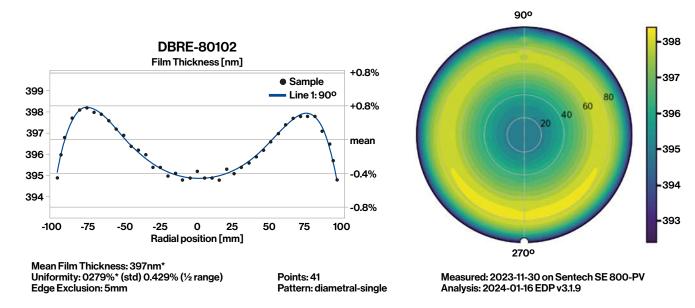

To illustrate the perfromance of the module, alumina films with thickness up to 100 nm were prepared at 200°C. Figure 2 illustrates the attained homogeneity of refractive index (@633 nm) of a 45 nm thin layer.

The mean refractive index value is 1.65 at 633 nm with a uniformity of better than ±0.5%, with a layer thickness uniformity of <1%. These layers show carbon contents below 1 atomic percent.

Being a member of the single process module family of the CLUSTERLINE 200®, the new PEALD module can be combined with other modules, e.g. metal layers by sputtering to realize any desired combination of layers on one cluster tool without breaking vacuum. Tools configured in that way can be used to achieve layer stacks of various thin film materials, e.g. piezo-active systems with an oxide capping layer.

#### **Get in touch!**

Are such combinations of various techniques on one single platform missing in your tool portfolio?

Does this versatile module fit into your existing CLUSTERLINE® 200 units, or are you considering a cluster just with PEALD modules? We will be happy to discuss the various options with you!

Figure 2: Refractive index uniformity of a 45 nm thin layer of  ${\rm Al_2O_3}$  prepared by PEALD

#### Why Evatec PEALD?

### Excellent conformality:

Homogeneous film thickness, even on complex geometries.

## Precise thickness control:

ldeal for very thin films.

#### Consistent film properties:

Ensuring optimal material quality.

#### Flexibility:

Integration of PEALD module alongside PVD, PECVD & etch on CLUSTERLINE® 200.

**Process characteristics and module features**

Deposition pressure:

2·10<sup>-3</sup> – 0.2 mbar

Plasma excitation:

ECR @ 2.45 GHz

Gas lines:

Up to 9

Precursor vessels:

2 or more

#### Want to know more?

111111

11111111111111111

Not familiar with the CLUSTERLINE® platform? Then why not watch the short CLUSTERLINE® family video to learn about Evatec's range of solutions on 200, 300 and 600mm.

To learn more about PEALD contact your local Evatec office

## Moving made easy: Seamless machine relocation for your Evatec equipment

At Evatec, we understand that moving your valuable thin film equipment can be a daunting undertaking. Downtime disrupts production schedules and can significantly impact your bottom line. That's why we've carefully designed a comprehensive equipment relocation service to minimize disruption and ensure a smooth transition. *David Dietsch*, Product Marketing Manager Customer Service, takes you through everything you need to know about our service, complete with a real-life example to illustrate the process.

#### Planning is paramount

The key to a successful machine move is careful planning. Our team of experienced and certified field engineers will work closely with you to create a customized relocation plan. Every detail is considered, from the initial pre-inspection to the final handover. This collaborative approach ensures a seamless and efficient process, minimizing downtime and maximizing productivity.

#### Benefits of utilizing Evatec's relocation expertise

When you choose Evatec for your machine relocation needs, you gain access to several compelling benefits:

■ Detailed planning and preparation:

We work hand in hand with you to

develop a comprehensive plan that

covers all aspects of the relocation.

From pre-dismantling checks to recommissioning at the new site, we leave

no stone unturned.

#### **■** Tailored options:

Recognizing that every relocation is unique, we offer three levels of service: Light, Standard, and Full. Choose the one that best suits your specific needs and budget.

#### ■ Unwavering support:

Our team remains by your side throughout the entire process. Should any unforeseen issues arise, we address them promptly, ensuring a seamless relocation experience.

#### **■** Experienced professionals:

Our relocation specialists have extensive experience in handling your equipment. You can rest assured that your valuable equipment is in capable hands.

| OPTIONS                                | LIGHT    | STANDARD   | FULL     |

|----------------------------------------|----------|------------|----------|

| Planning / preparation tool relocation | <b>⊘</b> | <b>⊘</b>   | <b>⊘</b> |

| Pre-checks on and off site             | <b>⊘</b> | <b>⊘</b>   | <b>⊘</b> |

| Health check                           | ×        | <b>⊘</b>   | <b>Ø</b> |

| Baseline data collection               | <b>⊘</b> | <b>⊘</b>   | <b>⊘</b> |

| Decommission of equipment              | <b>⊘</b> | $\bigcirc$ | <b>⊘</b> |

| Organization of transport              | ×        | ×          | <b>⊘</b> |

| Re-installation                        | <b>⊘</b> | <b>⊘</b>   | <b>⊘</b> |

| Start up                               | <b>⊘</b> | <b>⊘</b>   | <b>⊘</b> |

| Functional test and handover           | ×        | $\bigcirc$ | <b>Ø</b> |

#### Your role in the relocation process

While Evatec manages the relocation itself, your cooperation is crucial for a successful transition. Here's how you can contribute:

#### ■ Review of consumables:

Work closely with our team to assess the remaining life of consumable parts within the equipment. This assessment will help determine if replacements are needed before or after the move.

#### ■ Site support:

Leverage your team's expertise during the isolation, connection, and testing phases at both the original and new locations.

#### ■ Transport equipment:

The necessary transport equipment will have been provided during the initial system installation. However, you are ultimately responsible for transporting the equipment to the new location.

#### Considerations for obsolete parts during a relocation

Relocating equipment that is 7 years old or more can be a concern, especially if you suspect it contains obsolete parts. Evatec understands these challenges and offers guidance to ensure a smooth transition for your legacy equipment. Here's what we recommend when dealing with potentially obsolete parts during a move:

#### **Consumables: Planning for replacement**

Consumables, such as gaskets and O-rings, are essential to maintaining proper sealing and functionality within your equipment. Over time, these parts can degrade and lose their effectiveness. When relocating older equipment, it's important to consider the age and condition of consumables. Evatec recommends proactive replacement planning.

Consumables, especially those that are not replaced for long periods of time, can lose their elasticity and sealing properties. This can lead to leaks, contamination, and potential damage to equipment during transport or recommissioning. Ensuring that replacements are available in advance avoids delays and ensures a smooth restart at the new site.

#### Consideration of obsolete parts: A holistic approach

We recommend looking at the relocation process as an opportunity to take a holistic approach to obsolete parts. Here's why:

#### ■ Uncertain functionality:

There's a chance that obsolete components, especially after the stress of transportation, may fail to function when restarted. Proactive replacement during the move minimizes downtime and ensures optimum performance at the new location.

#### ■ Retrofit efficiency:

Replacing obsolete parts during the relocation offers significant efficiency benefits. With the equipment already decommissioned and readily accessible, retrofit installation becomes a more streamlined process compared to retrofitting at a later date.

#### Evatec support: Retrofits before re-installation

To maximize efficiency and minimize downtime, Evatec recommends that all necessary retrofits are in place before the move begins. Our team can assist you in identifying the appropriate replacement equipment and ensure that it is installed at the new site during the re-installation phase. This proactive approach streamlines the relocation process and ensures that even your legacy equipment will also perform optimally in the new location.

By following these recommendations and utilizing Evatec's expertise, you can relocate your older equipment with confidence, even if it contains obsolete parts. We'll work with you to ensure a smooth transition, minimize downtime, and breathe new life into your valuable machines.

#### Our relocation service in action: A customer story

Picture this: A cutting-edge sputter tool nestled in its original facility, humming with precision and purpose. But change is afoot – the customer has decided to relocate it to a brand new, state-of-the-art production line. The stakes are high; even a small hiccup in the process could disrupt their carefully orchestrated production schedule. So, they opt for our Standard Relocation Package and take care of the transport themselves.

#### Planning the move

Our team goes into action, working closely with the customer's engineers. Here's what happens:

#### ■ Site check:

We meticulously examine the entire transport route, from loading ramp to destination. Together with the customer, we ensure that there are no spatial constraints along the transport route. We also check that the new site meets the equipment's facility requirements.

#### ■ Health check:

Think of it as a thorough medical examination for the sputtering tool. We assess critical components, run backups, perform visual checks and identify any maintenance required. After all, a healthy tool is a reliable tool.

#### ■ Baseline data collection:

We collect baseline data - a reference point for assessing the performance of the tool after installation. This data becomes our compass along the way.

#### The relocation process

Once the planning phase is complete, the relocation dance begins:

#### **■** Decommissioning:

Carefully and deliberately, we say goodbye to the sputtering tool in its original home. Utilities are disconnected, process cooling water is drained, and cables are marked for quick identification during installation. Each component is secured for the journey ahead.

#### ■ Transportation:

The customer steps in and provides the initial transport equipment. They orchestrate the tool's safe journey to its new home - the gleaming production line awaiting its arrival.

#### ■ Re-installation:

Our engineers perform a ballet of precision. The sputtering system pirouettes into the new facility, perfectly aligned with the utility connections. Daily progress updates flow like choreography notes to ensure everyone stays in sync.

#### Start-up and handover

As the curtain rises on the final act:

#### ■ Start-up:

The tool awakens, following established procedures. Systems initialize, gas lines purge, and functional checks dance across the stage. It's showtime!

#### ■ Functional testing:

Extensive tests unfold to ensure the sputtering tool is operating within optimal parameters. The audience - our customers - hold their breath in anticipation of a flawless performance.

#### ■ Baseline data comparison:

Our service engineers revisit the health check points. Is the system as vibrant as before? The answer is in the data.

#### ■ Handover:

The grand finale! With all systems verified, we formally present the tool to the customer's production team. Detailed documentation accompanies the handover, like a backstage pass to operational changes. The customer steps into the spotlight, ready to qualify the sputter tool's role in their production once again.

#### **Considering relocation?**

Are you considering relocating your valuable thin film equipment? Don't let the process become a roadblock.

Evatec's relocation services can:

- ☑ Ensure a smooth transition

- ☑ Minimize downtime

- ☑ Maximize your productivity

Contact your local Evatec Sales and Service organization today and let us start planning your move.

**Spare Parts**

**Support**

**Training**

Retrofits

#### **Evatec's services**

Watch our video to learn more about our portfolio of services that will help you get the most out of your Evatec tool.

## ECL – Supporting customers with small scale production & thin film characterization services

Head of Evatec Competence Laboratory *Philip Zeller* gives us an update on the latest capabilities in the ECL and how we are now expanding the services available to customers helping them not only with technology development and prototyping, but also small scale production and quality control in their daily business.

#### ECL - Ready to support customers in deposition and characterization

Evatec's ECL was established back in 2019 as a center for collaboration with technology partners and customers. It brought equipment and people together in an environment optimized for the best sample production, networking, information exchange and creative thinking. For the last 5 years, it has been a place where customers from around the world joined Evatec process engineers working together on the development and optimization of their next generation thin film processes.

And now it's time to make capabilities of ECL available to customers needing to characterize films deposited within their own facility where they don't have the metrology tools, or needing small scale production support, e.g. as an interim solution whilst they are busy ramping up their own production facilities.

#### ECL - A lab like a fab

The ECL is an easy place to work-housing both deposition tools and measurement equipment within a central measurement laboratory (EML).

At the heart of the ECL lies a portfolio of thin film tools with advanced control capabilities in a range of configurations to support applications across advanced packaging, power, wireless, MEMS, optoelectronics and photonics. System architectures are available to handle substrate sizes up to 650mm x 650mm.

Table 1 summarizes the range of tool architecture and typical processes available within the fab.

#### **Tool architecture** types

- Batch

- Cluster

- Inline

#### **Process** technologies

- Etch

- PECVD

- PEALD

- Sputter

- Evaporation

#### **Substrate** handling / loading

- Manual

- Cassette-tocassette

- AFEM

- Single wafer processing

- **Batch** processing

#### **Processes**

- Dielectrics

- TCOs

- Metals

- Piezoelectrics

- Soft magnetics

#### APC capabilities

- Plasma **Emission Monitoring** (PEM)

- Broadband **Optical Monitoring** (GSM)

Table 1: Summary of ECL capabilities

#### Thin film characterization and quality control

The EML is a hub for metrology experts.

Equipped witht tools ranging from basic mechanical profilometers to advanced instruments like AFM, SEM, XRD and XRF, the EML has constantly enhanced its capabilities for advanced characterization of the deposited thin films.

The AFM provides detailed surface topography information with sub-nanometer resolution.

XRD offers insights into crystalline grains within a film, enabling the determination of crystal structure, lattice distance, grain width, crystal quality, and orientation. Additionally, we can measure instrument pole figures and reciprocal space maps for more sophisticated film structure analysis.

X-Ray Reflectometry allows us to measure film thicknesses (typically from a few up to 150nm) and roughness, including multilayer systems and their buried interface roughness.

XRF enables precise, non-destructive film thickness measurements in the sub-nanometer range and provides information about the elemental composition of a sample.

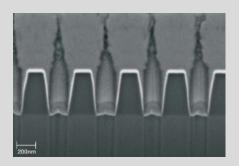

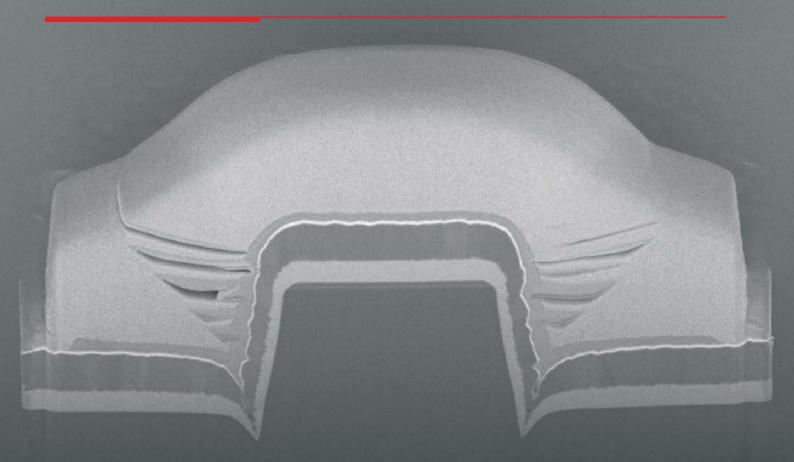

The latest addition to the metrology lab is the Zeiss FIB-SEM. This tool allows us to capture images with information on the topography and the composition of a sample. In combination with its Focused-lon-Beam (FIB) it allows us to capture images of structures such as trenches and vias and analyze the conformity of the deposited films. Figure 1 illustrates a typical case study.

The EML and its measurement tools are all conveniently located at the heart of the ECL.

The full range of metrology techniques available to customers is illustrated in Table 2.

#### The ECL - A perfect production environment

Needless to say, the ECL is the perfect production environment of 3000 square meters with a range of clean room spaces down to ISO 4 and particle levels are measured online to maintain a consistent environment. Highly experienced Evatec staff operating the deposition equipment and making thin film characterization measurements on behalf of customers have access to the expertise of Evatec's application and process engineers.

#### Figure 1: Case Study - Analysis of 3D structures

We observe silicon blind vias covered by a tantalum layer, which appears as the brightest element in the picture. This tantalum layer was deposited using our advanced long-throw sputtering configuration.

Although the FIB/SEM technique does not match the resolution of TEM, its significantly faster processing speed makes it invaluable. Possessing this metrology tool in-house enables us to perform exceedingly efficient and rapid optimizations of sidewall and bottom coverage, a critical advantage as feature sizes diminish and IC designs evolve into three-dimensional structures.

| Method                                                            | System                                                                                                | Characterization of                                                                       | Sample size     |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|

| Atomic Force Microscopy (AFM)                                     | Park Systems NX20                                                                                     | Topography, surface roughness                                                             | Up to 200mm     |

| X-Ray Diffraction &<br>Reflectivity (XRD & XRR)                   | Bruker D8 discover                                                                                    | Crystallinity & crystall orientation, thickness (5 - 150 nm), density                     | Up to 300mm     |

| X-Ray Fluorescence<br>Spectroscopy (XRF)                          | Rigaku XRF                                                                                            | Composition, thickness (sub nm - mm)                                                      | Up to 300mm     |

| Scanning Electron<br>Microscopy (SEM) /<br>Focused Ion Beam (FIB) | Zeiss Crossbeam 550 L (Gemini II)                                                                     | Topography, cross section / resolution:<br>2 nm / magnification 12x- 2E6x                 | Up to 300mm     |

| Electron Dispersive X-Ray<br>Spectroscopy (EDX)                   | BRUKER QUANTAX EDS (Xflash 410)                                                                       | Composition                                                                               | Up to 300mm     |

| Ellipsometry                                                      | Woollam SE M-2000F / Sentech<br>500Adv, SE 800-PV & SENResearch<br>4.0                                | Optical properties (n,k), thickness (1 nm - 10 $\mu$ m) / (wavelength range: 245-2500 nm) | Up to 300mm     |

| 4 point probe                                                     | 4Dimensions Polytec 333A DI V5.5R1/<br>4Dimension 280 TCI & 280 BM 1003 /<br>KLA-Tencor OmniMap RS100 | Sheet resistance (0.001 - 8E11 Ω/Sq)                                                      | Up to 300mm     |

| Spectrophotometry                                                 | Perkin Elmer Lambda 950, 750,<br>Spectrum II / Essentoptics GmbH<br>Photon RT                         | Transmission, reflection (wavelength range: 175 - 3300 nm & 1200 - 28500 nm)              | 50 x 50mm       |

| Reflectometry                                                     | ProMicron NanoCalc 300 / Mikropack<br>Metrology Systems NanoCalc 2000                                 | Film thickness (10 nm - 20 $\mu$ m) / wavelength range: 210 – 2500 nm                     | Up to 300mm     |

| Laser level & Interferometry                                      | Frontier Semiconductor FSM 128L /<br>KLA-Tencor Flexus FLX 2320 / Toho<br>Technology FLX 3300-T       | Wafer bow, radius, stress (1 - 4 gpa) / dual-laser                                        | Up to 300mm     |

| Optical Microscopy                                                | ProMicron Leica INM 200                                                                               | Particles (sensitivity:1µm)                                                               | Up to 200mm     |

| Laser Light Scattering                                            | UnitySC Lightspeed / NanoPhotonics<br>Reflex 300 TT 150                                               | Particles (sensitivity: 50 nm) / haze                                                     | Up to 300mm     |

| Contact Stylus<br>Profilometry                                    | Veeco Dektak V 300 Si & V 150 /<br>KLA-Tencor Alpha Step 500 & 600,<br>P 16                           | Thickness (1 nm - 1200 µm) / stress                                                       | Up to 300mm     |

| Profilometry                                                      | Eichhorn & Hausmann<br>MX 204-8-21 V                                                                  | Wafer thickness, bow, warp,<br>TTV (Total Thickness Variation)                            | Up to 200mm     |

| Magnetometry                                                      | Shb Instruments MESA 200 (in-plane) / Kerr magnetometer (self-made)                                   | Magnetic properties                                                                       | Up to 200mm     |

| Contact Angle                                                     | Krüss FM40MK2 Easy Drop                                                                               | Surface tension                                                                           | Up to 100x100mm |

| Life timer                                                        | Sinton WCT120 &<br>Suns-Voc 150                                                                       | Life time of charge carriers in Si                                                        | Up to 200mm     |

Table 2: A wide ranging list of Thin Film characterization techniques

#### Want to know more?

To learn more about the new services available and to get a quote please email: **philip.zeller@evatecnet.com**

Our market organization is ready to serve you!

As of January 2024, Evatec embarked on an exciting new chapter. With the launch of our market- and product-focused organization, we have united customer-centric strategies and market orientation with cutting-edge equipment and process development under one roof. This new structure strengthens our ability to deliver tailored, innovative solutions and exceptional support across the fields of Compound and Photonics, as well as Semiconductor and Advanced Packaging. *Ralph Zoberbier*, *Admir Asanoski* and *Jakob Bollhalder* introduce our business fields and their activities.

We are more than happy to introduce Evatec's new organizational structure, which unites our strengths from previous business units with product development, customer engineering, and process innovation. This strategic integration allows us to better support your journey within two dedicated sectors of the electronics industry.

In the Compound and Photonics business field, we are focused on pioneering solutions for Optoelectronics, including LEDs and laser diodes, MEMS, and Wireless technologies like BAW and SAW filters. In addition our work is particularly driven by the latest developments in augmented and virtual reality layers, as well as the growing demand for photonic integrated circuits.

In Semiconductor and Advanced Packaging, we offer cuttingedge technologies for front- and backside layers of Power Devices, advanced packaging solutions, and heterogeneous integration applications. As the industry advances, we are committed to also delivering the innovative technologies needed to overcome challenges in frontend integration and panel processing, which are crucial to meeting the performance demands of Artificial Intelligence (AI).

You can read more about our developments and acheivements in the next two chapters of this edition of LAYERS.

>>>>

#### Compound & Photonics – Leveraging know-how across market segments to keep the lead!

Just like within semiconductor and advanced packaging, huge changes in technology are and will continue to enable the mass market introduction of exciting new consumer devices. **Jakob Bollhalder**, Head of Compound & Photonics, introduces the primary market segments and the technological innovations propelling growth.

#### **Key Market Segments and Drivers**

- Within **Wireless Communication**, enhanced capabilities using 5G are already a feature of the smart devices in our hands and the drive is already on to deliver even faster speeds, lower latency, and greater connectivity 6G here we come!

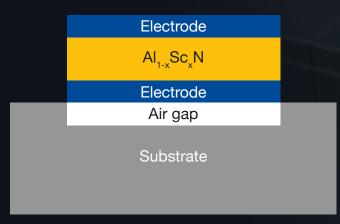

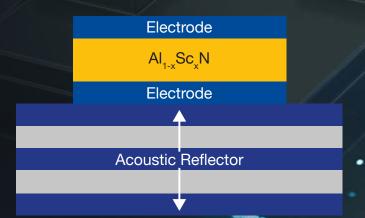

- ☑ From high performance SiO₂/SiN insulating layers to AIScN piezoelectrics for filtering and metal electrodes Evatec is supporting advanced SAW (Surface Acoustic Wave), BAW (Bulk Acoustic Wave), and RF Power technologies.

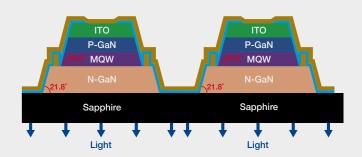

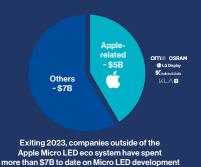

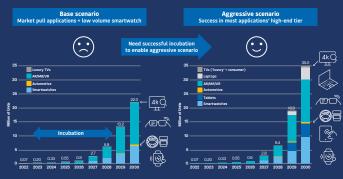

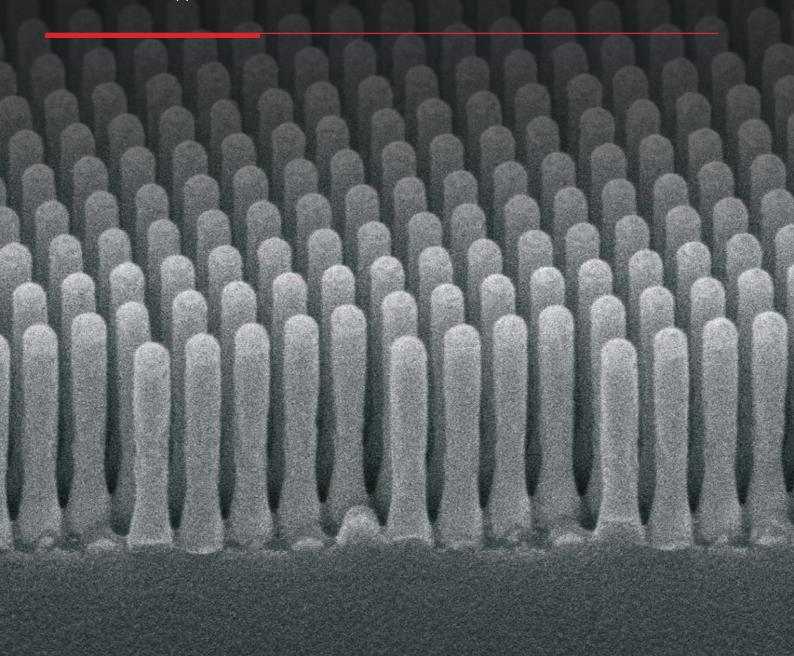

- Technologies within **Optoelectronics** like Micro LED Displays will see significant growth through mass market applications, initially in wearable technology, then expanding into augmented reality (AR) and automotive displays.

- ☑ From low-damage TCOs that reduce fabrication damage and improve device longevity, to metal contacts ensuring reliable electrical connections, and mirrors that enhance light manipulation and efficiency, Evatec's solutions are trusted by the world's leading manufacturers. Additionally, our anti-reflective coatings significantly improve output.

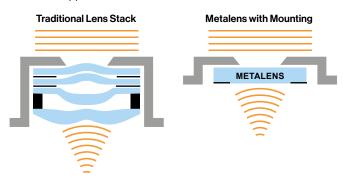

- **Photonics** is a sector with huge opportunities for the future and the integration of photonic components on a single chip. Photonic Integrated Circuits (PIC) is just one approach that will revolutionize performance and costs for many new consumer applications.

- ☑ Successful market introduction calls for thin film production solutions in areas like input couplers, e.g. BTO or for integrated light connections (e.g. SiN) and Evatec is your partner!

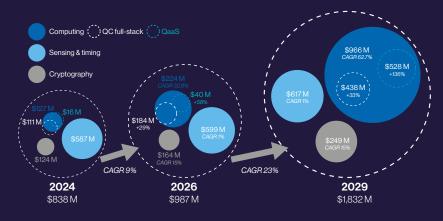

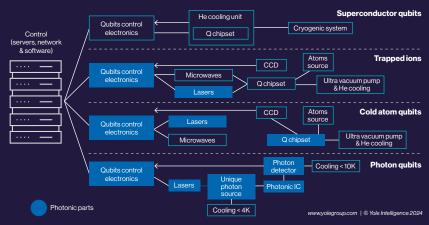

- MEMS (Micro-Electro-Mechanical Systems) technology offers significant growth potential in areas like Magnetic Sensing: (new advances in actuation technologies) and Quantum Computing (advanced materials and precise fabrication techniques)

- ☑ In the realm of quantum computing in particular we offer know-how for superconducting films such as Nb, aTa, AI, and Ti. Pilot lines established with market leaders means Evatec is well placed to support the industry as it takes off at the end of the decade.

#### Who is Evatec...

#### Why choose Evatec as your partner?

Listening to and innovating together with our customers is at the heart of our philosophy. Just like market needs develop so must our production solutions. That means providing platforms inherently flexible by design which can be adapted as necessary to the changing needs of individual customers, be it higher throughputs, more demanding layer specifications and sometimes both! Working together with our customers and suppliers in long term partnership is a "win-win" for us all.

Our aim is simple – to deliver the best customer value in the industry.

#### Semiconductor & Advanced Packaging – A great place to be!

In the ever-evolving landscape of electronics, the Semiconductor & Advanced Packaging sector is a hugely exciting area of innovation and growth. Admir Asanoski, Head of Evatec's business in this sector guides us through some of Evatec's activities covering three market segments, each with its own technological advances and market drivers.

#### **Key Market Segments and Drivers**

- Power Devices such as transistors, diodes, and thyristors are essential for a myriad of electronic systems. The demand for these devices is surging, driven by the electrification of transportation, the integration of renewable energy, and stringent energy efficiency regulations. These components are integral to the functionality of electric vehicles, solar and wind power systems, and energy-efficient consumer electronics.

- ☑ Evatec leads the way with a diverse range of metallization processes for power devices made from Si, SiC, or GaN. Our portfolio includes solutions for frontside and backside contacts, protection layers, and other applications, all tailored to meet the specific needs of our customers.

- Within the Frontend Market our focus is on advanced node devices, such as Logic ICs and Memory products, driven by the ongoing trend towards miniaturization and integration. The demand for advanced CMOS ICs is fueled by the need for smaller, more powerful, and energyefficient devices, as well as the requirements of AI and big data analytics.

- ☑ Evatec offers interconnect metallization processes and niche applications such as warpage compensation used within the process flow of a 3D-Nand Memory, ensuring the highest quality and reliability in end products.

- Advanced Packaging techniques are revolutionizing the performance of semiconductor devices by integrating multiple components into a single package. Employing technologies like 2.5D and 3D integration, WLP, and PLP brings greater miniaturization and enhances electrical and thermal performance.

- ☑ As market leader, Evatec delivers sputter solutions for advanced packaging processes with a unique system concept for wafer-level packaging delivering industry-leading R performance and outstanding CoO. With more than 10 systems installed around the globe our solutions for panel-level packaging, including Fan-Out processes and TGV, are at the forefront of IC panel advances.

#### **Our Mission**

#### Teamwork

Collaborate to achieve success

Drive and foster innovative solutions

#### Responsibility

Take ownership of our actions

#### Committment

Consistently deliver on our promises

#### Integrity

# SEMICONDUCTOR & ADVANCED PACKAGING NEWS

| 36 | Advanced Packaging   PCB / IC-Substrate – Reducing the environmental impact Gernot Schulz & Christof Wernbacher, AT&S & Roland Rettenmeier, Evatec                                                                     |  |  |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 40 | Advanced Packaging   CLUSTERLINE® 600 & next generation IC-substrates Roland Rettenmeier                                                                                                                               |  |  |  |

| 44 | Advanced Packaging   Cross-Contamination in Multi-Chamber PVD Systems Kay Viehweger, Fraunhofer IZM-ASSID & Dr. Patrick Carazzetti, Evatec                                                                             |  |  |  |

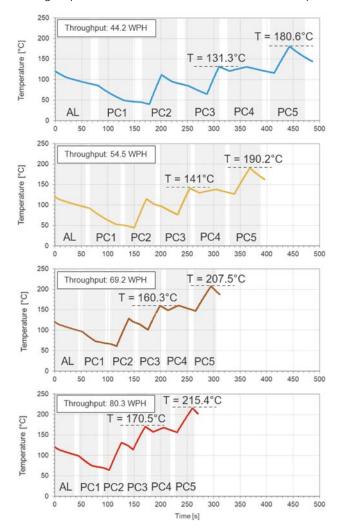

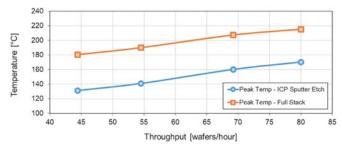

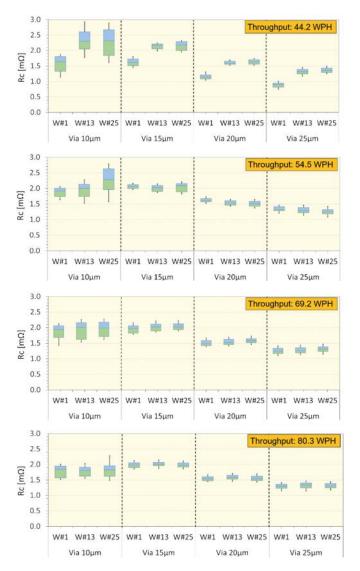

| 52 | Advanced Packaging   HEXAGON – Optimum R <sub>c</sub> Control & productivity  Kay Viehweger, Fraunhofer IZM-ASSID & Dr. Carl Drechsel, Dr. Patrick Carazzetti, Carl Wang,  Dr. Juergen Weichart & Ewald Strolz, Evated |  |  |  |

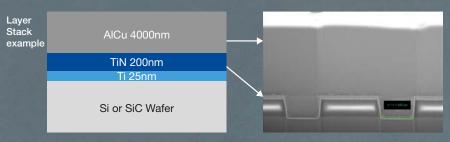

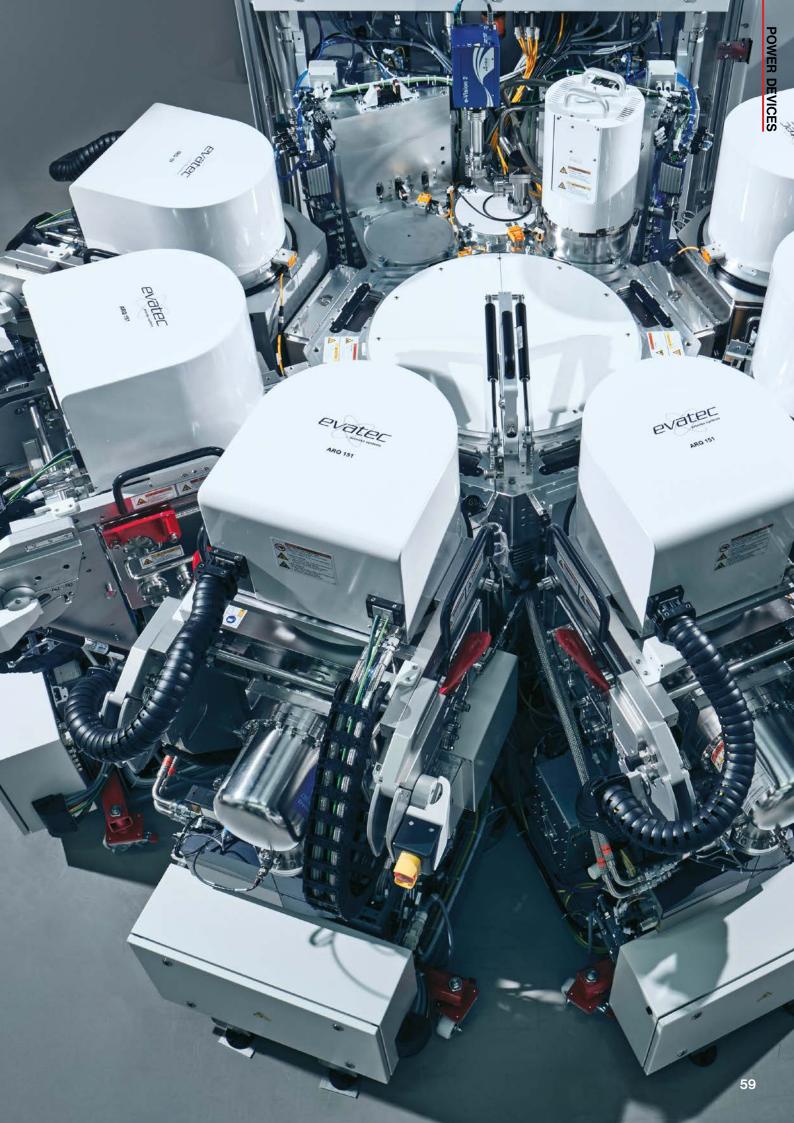

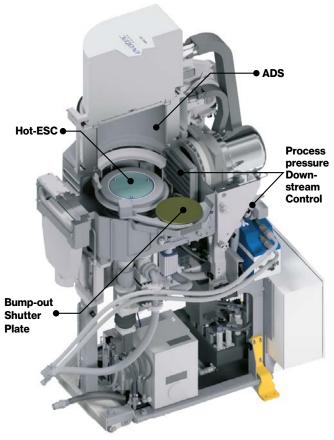

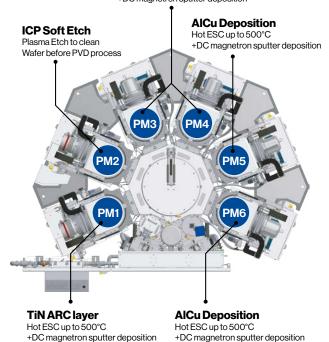

- Power Devices | Frontside Processes Trench filling & Planarization Fabian Kramer & Mohamed Elghazzali

- Power Devices | Power ICs: New Cu Frontside processes on 300mm Mohamed Elghazzali

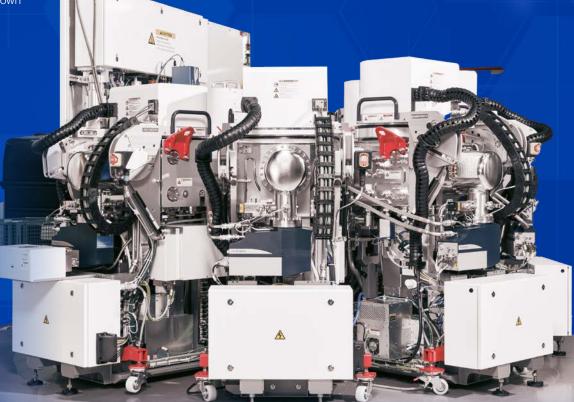

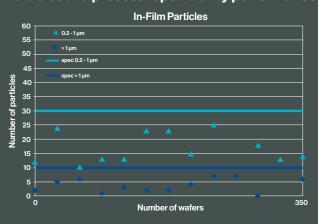

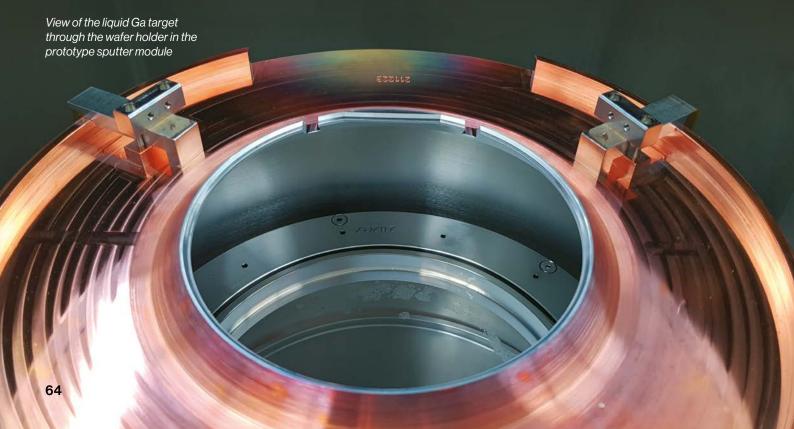

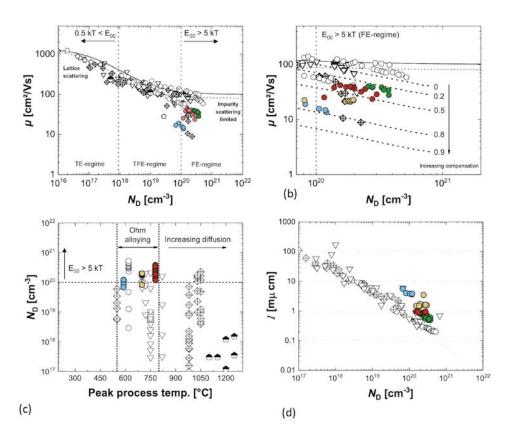

- Power Devices | Investigating GaN sputter from a liquid Ga target

Dr. Philipp Doering, Fraunhofer Institute for Applied Solid State Physics (IAF) & Thomas Tschirky, Evatec

- Power Devices | HEXAGON double up in power device applications

Fabian Kramer & Gerald Feistritzer

## Reducing the environmental impact in the PCB / IC-Substrate industry

AT&S experts *Gernot Schulz* and *Christof Wernbacher* togther with Evatec's *Roland Rettenmeier* explain how the CO<sub>2</sub> footprint of PCB manufacturing can be reduced by reducing raw materials and wet processes, optimizing product build ups and introducing dry processes.

#### AT&S - Playing its part

The Electronics industry as well as the PCB industry are undergoing a massive change in manufacturing. Governments, OEMs and customers all require a reduction of the CO<sub>2</sub> footprint and a resource-efficient use of raw materials, support materials, energy and water throughout the entire value/supply chain. The "Green Deal" is the European Union's response to this major global challenge for the future. Manufacturing companies are among the key players in the environmentally friendly economic development of tomorrow and are called upon to contribute to solving these challenges with their ideas and innovations. Various measures are available for this purpose: Switching to renewable energy, climate-friendly mobility, resourceconserving value chains, material innovations and intelligent product developments that are designed entirely for recycling.

### Product Carbon Footprint – Wet chemical processes are the main contributor

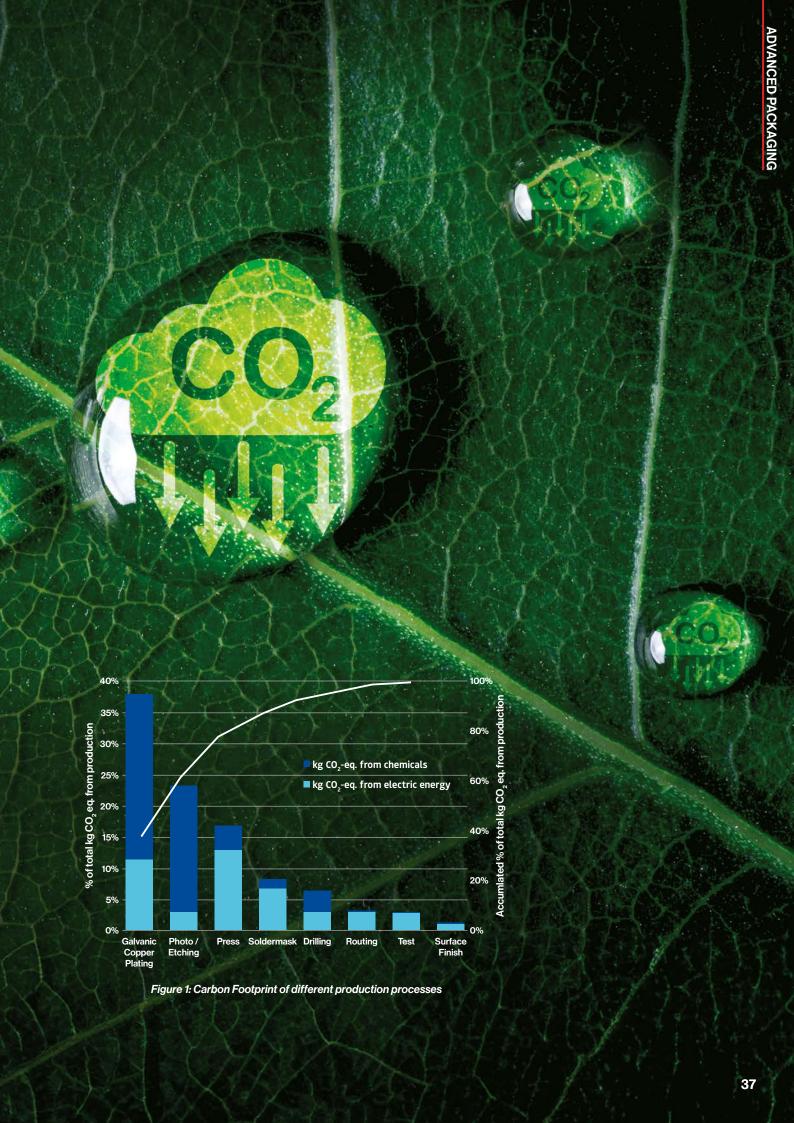

The production process of printed circuit boards generally consisting of mainly wet chemical processes such as etching, galvanic or cleaning. Figure 1 gives an overview on how different production processes from classic PCB production contribute to the overall Product Carbon Footprint of PCB (PCF). Therefore, a sample product consisting of a 10-layer PCB with PTH and Laser Drills manufactured in AT&S production facility in HTB was chosen for this study. Several Energy and Chemical consumptions along the production chain were measured and broken down on product level. The contribution of the different process steps is highly dependent on PCB design such as number of layer, complexity and advanced technologies

used. In general a significant amount of emissions are related to the energy and chemical intensive galvanic and etching process steps. Both are standard processes within the PCB production landscape and form the basis of a subtractive manufacturing approach. Since sustainability is in addition to costs and technology becoming a further focus point, additive manufacturing approaches which do not rely on wet chemical processes are becoming of greater interest.

One important part and door opener into additive manufacturing is the sputtering / PVD process. On one hand it improves PCB manufacturing from a technology point of view, on the other hand it allows us to reduce the amount of subtractive production processes.

#### Novel technologies as a key to more sustainable products

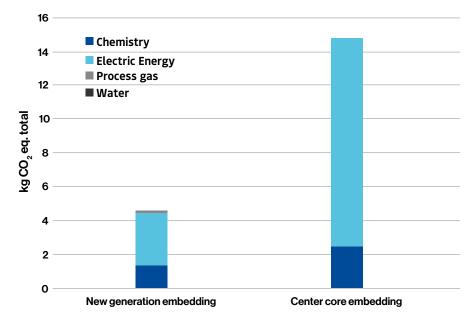

To further substantiate this correlation, a study was initiated which allowed direct comparison of the environmental footprint between a PCB produced with Sputtering/PVD processes on Evatec's CLUSTERLINE® 600 versus a PCB produced with standard technology. This study was done as part of AT&S' initiative to better understand the environmental impact of different technology platforms and process groups. Therefore, the boundaries of the study were set around processes dedicated to a specific technology. The focus of the study was so called embedding technology, which allows the embedding of ICs as well as active and passive components directly into the PCB which gives numerous advantages especially from a technological point of view. Different technology levels are available with Center Core Embedding (CCE) being the current standard technology. The more sophisticated technology which is currently under development uses a Sputtering/PVD process.

For the comparison the main process steps of both technologies were quantified regarding their consumption of energy, chemicals, process gas and water. The environmental impact of the different input streams was assessed with a combination of primary data from material and energy supplier as well as data from ecoinvent database.

Figure 2 shows the comparison of the Carbon footprint between both technologies. The new generation embedding technology shows a significant reduction, mainly due to a reduction of energy and chemical consumption. This reduction can be achieved because of the more efficient product design becoming feasible with new technology. The process gas which is only used in the new generation embedding technology does not have a serious impact on the overall result.

As an additional benefit, which is not considered in the assessment, the new generation embedding technology also increases the utilization of the panel according to the die to package ratio, which basically indicates how densly the Integrated Circuits (IC) can be placed onto

the Package. Considering this improvement, the advantage of the new technology is even more significant.

In addition to embedding technology, Sputtering/PVD processing has the potential to increase the opportunities in PCB design not only in terms of technological aspects, but also in terms of more sustainable design. Different Life Cycle Assessments of PCBs have shown that reducing layer counts as well as reducing the size of a single PCB for better utilization of the production panel leads in most cases to a significant improvement of the Product Carbon footprint.

#### Improvement beyond carbon footprint

The focus of the industry and branch in Europe is definitely on reduction of the carbon footprint due to the several large initiatives such as the EU Green Deal or the Paris Agreement which are focusing on Greenhouse gas reduction. But to gain a holistic picture of environmental impact it is also necessary to take a look on further influences (for example environmental impact categories according to CML-2016). For all these categories beyond the carbon footprint AT&S plans to extend these assessments to create a more complete picture. But especially for PVD/ Sputtering process and the opportunities coming with this technology an even larger improvement is expected than for the carbon footprint, since the reduction of wet chemical processes and therefore chemistry usage is highly connected to other benefits e.g. reduction human toxic substances, acidification potential or nutrification potential. Due to the fact that Sputtering/PVD is also considered as one key technology for miniaturization of electronic components such as PCB or IC Substrates, it can also make its contribution to reducing the global e-waste problem. With miniaturization approaches the relative amount of e-waste can be reduced by simply reducing the volume and mass of the electronic components. Overall more dry process steps in PCB production will lead to less impact on the environment from the industry sector.

Figure 2: Carbon Footprint of new generation embedding technology compared to standard embedding technology

#### Heading in the right direction

The PCB industry has been trying to find novel technologies and processes to reduce the amount of wet chemical subtractive processes within the manufacturing landscape since many years. The internal and external pressure to reduce the environmental footprint of PCB production is now bringing an additional argument to go in this direction. Sputtering/PVD process technology now seems to be the most promising approach. Direct comparison with conventional technology shows a significant improvement from both sides ecologically and technologically. Currently the technology is used for special use high end cases, but when it finds its way to more commodity use cases also high volume applications can profit from the environmental impact reducing processes.

#### **CLUSTERLINE® 600**

To read about Evatec's CLUSTERLINE® 600 sputter platform and some of the most recent technological developments go to page 40 or visit **evatecnet.com/products/clusterline-family/clusterline-600**

#### A view of AT&S\*

Technology and digitalization are having an ever-growing impact on our lives and are increasingly shaping our daily routines at home and at work. The advances achieved in these fields in recent years are truly breathtaking and have created crucial momentum for growth in every sector of the economy. As a global technology enterprise, AT&S is actively involved in these developments and plays a decisive role in shaping the digital world of tomorrow. This also represents an enormous responsibility, which AT&S has always accepted and fulfilled through its forward-looking vision, pioneering investments in research and development, and responsible use of resources. The high-end PCBs and IC substrates AT&S supplies influence future industry standards, products and applications in a number of key industries.

Want to know more? Visit https://ats.net/en/or complete the contact form at https://ats.net/en/contact/

\*Source: AT&S website

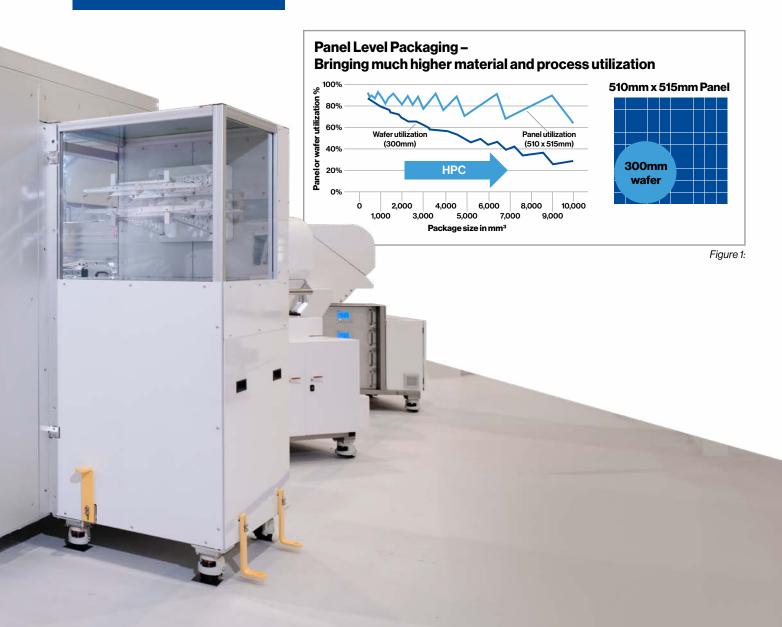

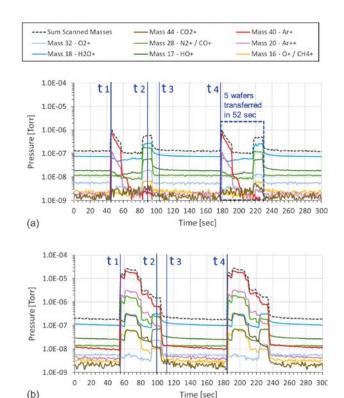

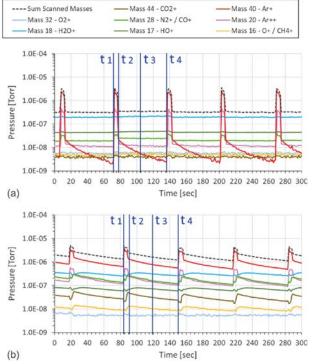

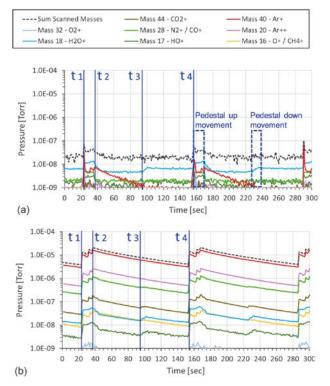

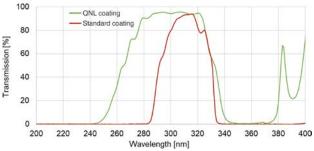

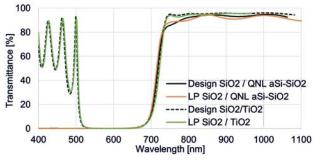

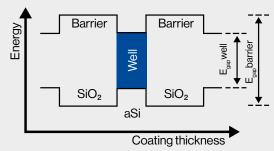

## CLUSTERLINE® 600 Perfect for next generation IC-substrates too!